CHASSIS 712A SUPPLY UNIT (NETZTEIL SM)

AT 349354065

This is a SMPS Supply unit which seems simple but is not !

- 3 SUB Units are composing the FINAL device unit

1 - MAINS RECTIFIER + DEGAUSS PTC + BOBBIN FILTERS + CAPS (burned !! !!!) BS422

ET 309378996 (NETZEINGANG)

2 - Pulse Command unit with S417T (Telefunken) BS423 AT349354067 (ANSTEUERUNG)

3 - Secondary Voltages Generation and separation (With a LM317) BS426 AT349354068

(SEC.SPANNUNGSERZEUGUNG).

- CHROMA IA (1) with TDA2150 (Telefunken) BS202 AT349354052

- CHROMA II (2) with TDA2160 + TDA2140 (Telefunken) BS302

- Synchronization BS531 AT349354014 with ITT TBA950X2

- Frame Oscillator BS451 AT349354015

- Frame deflection output amplifier BS491 AT349354016 with BD312T + 2N5877T

(Motorola + Fairchild)

- E/W Correction unit BS501 AT349354017

- RGB ENDSTUFEN RGB OUT BS333 AT349354063

- TON ENDSTUFE SOUND UNIT BS151 AT349354008

- if video unit BS104 AT349 354 105.

Search and Tuning drive circuitry.

- BS33 (UAA170 Siemens + UA741 Texas Instruments + CD4011 RCA) Display search

- SPP core unit with AY-3-8203 (General Instruments) + MSM4956 (General Instruments)

+ ER1400 EAROM (General Instruments)

- RECEIVER 5000 With U318M (Telefunken) BS48 AT349370969.

TELEFUNKEN PALCOLOR 8848J QUARTZ MEMORY / TELEFUNKEN CHASSIS 712A DPS2 Drive circuit for an infrared remote control transmitter:

An infrared remote control transmitter includes at least one infrared light-emitting diode poled with respect to a point of reference potential so as to be conductive in response to voltages having the opposite polarity of a DC supply voltage and to be nonconductive in response to voltages having the same polarity as the DC supply voltage. A pus

h-pull amplifier is responsive to a pulse signal encoded to represent a remote control message to selectively couple the DC supply voltage or the reference potential to a capacitor coupled in series between the push-pull amplifier and the light-emitting diode. The capacitor is charged and discharged and an alternating drive voltage for the light-emitting diode having portions with polarities both the same as and opposite to the polarity of the DC supply voltage is generated. The push-pull amplifier is arranged so that when a component failure occurs, the portions of the alternating drive voltage having the polarity opposite to the polarity of the DC supply voltage are at least inhibited to prevent the continuous (i.e., DC) emission of infrared radiation.

h-pull amplifier is responsive to a pulse signal encoded to represent a remote control message to selectively couple the DC supply voltage or the reference potential to a capacitor coupled in series between the push-pull amplifier and the light-emitting diode. The capacitor is charged and discharged and an alternating drive voltage for the light-emitting diode having portions with polarities both the same as and opposite to the polarity of the DC supply voltage is generated. The push-pull amplifier is arranged so that when a component failure occurs, the portions of the alternating drive voltage having the polarity opposite to the polarity of the DC supply voltage are at least inhibited to prevent the continuous (i.e., DC) emission of infrared radiation. 1. In an infrared remote control transmitter for controlling a television system, apparatus comprising:

1. In an infrared remote control transmitter for controlling a television system, apparatus comprising:a reference circuit point for receiving a reference potential;

a supply circuit point for receiving a DC supply voltage;

a battery connected with a predetermined polarity connected between said supply and reference circuit points;

at least one light-emitting diode for emitting infrared radiation when rendered conductive, said light emitting diode having a cathode and an anode, one of said cathode and anode being connected to said reference circuit point, said light-emitting diode being poled with respect to said reference circuit point so as to be conductive in response to the application of a voltage to the other one of said cathode and anode having the opposite polarity to said battery with respect to said reference circuit point and non-conductive in response to the application of a voltage to said other one of said cathode and anode having the same polarity as said battery with respect to said reference circuit point;

a source cir

a drive circuit point;

a capacitor directly connected between said drive circuit point and said other one of said cathode and anode;

a diode directly connected between said other one of said cathode and anode and said reference circuit point and poled in the opposite sense to said light-emitting diode with respect to said reference circuit point;

push-pull amplifier means for developing a drive voltage at said drive point including first and second bipolar transistors of opposite conduction types, each of said transistors having a collector-emitter path and a base electrode for controlling the conduction of said collector-emitter path, said collector-emitter path of said first transistor being directly connected between said supply circuit point and said drive circuit point, said collector-emitter path of said second transistor being connected between said drive circuit point and said reference point; and

input means coupled between said source circuit point and said bases of said first and second transistors for rendering said collector-emitter path of said first transistor conductive and said collector-emitter path of said second transistor non-conductive in response to a first portion of said pulses of said input signal and for rendering said collector-emitter path of said second transistor conductive and said collector-emitter path of said first transistor non-conductive in response to a second portion of said pulses of said input signal.

2. The apparatus recited in claim 1 wherein:

three light-emitting diodes poled in the same direction are connected in series between said capacitor means and said reference circuit point.

3. The apparatus recited in claim 1 wherein:

a second capacitor is directly connected between said drive point and said other one of said cathode and anode in parallel with said first mentioned capacitor directly connected between said drive point and said other one of said cathode and anode.

a second capacitor is directly connected between said drive point and said other one of said cathode and anode in parallel with said first mentioned capacitor directly connected between said drive point and said other one of said cathode and anode.4. The apparatus recited in claim 1 wherein:

said input means includes a first capacitor connected between said source circuit point and said base of said first transistor; first means connected between said supply circuit point and said base of said first transistor for discharging said first capacitor; a second capacitor connected between said source circuit point and said base of said second transistor; and second means connected between said base of said second transistor and said reference circuit point for discharging said second capacitor.

5. The apparatus recited in claim 4 wherein:

said first means includes a further diode poled to be conductive when said collector-emitter path of said first transistor is non-conductive and non-conductive when said collector-emitter path of said first transistor is conductive; and

said second means includes a still further diode poled to be conductive when said collector-emitter path of said second transistor is non-con

ductive and non-conductive when said collector-emitter path of said second transistor is conductive.

ductive and non-conductive when said collector-emitter path of said second transistor is conductive.6. In an infrared remote control transmitter for controlling a television system, apparatus comprising:

a reference circuit point for receiving a reference potential;

a supply circuit point for receiving a DC supply voltage;

a battery connected with a predetermined polarity connected between said supply and reference circuit points;

three light-emitting diodes which emit infrared radiation when rendered conductive directly connected in series between a voltage application circuit point and said reference circuit point, all of said light-emitting diodes being poled with respect to said reference circuit point so as to be conductive in response to the application of a voltage to said voltage application circuit point having the opposite polarity to said battery with respect to said reference circuit point and non-conductive in response to the application of a voltage to said voltage application circuit point having the same polarity as said battery with respect to said reference circuit point;

a source circuit point for receiving an input signal having pulses encoded to represent information for controlling a predetermined function of said television receiver;

a drive circuit point;

a first capacitor directly connected between said drive circuit point and said voltage application circuit point;

a second capacitor directly connected between said drive circuit point and said voltage application circuit point;

a diode directly connected between said voltage application circuit point and said reference circuit point and poled in the opposite sense to said light-emitting diode with respect to said reference circuit point;

push-pull amplifier means for developing a drive voltage at said drive point including first and second bipolar transistors of opposite conduction types, each of said transistors having a collector-emitter path and a base electrode for controlling the conduction of said collector-emitter path, said collector-emitter path of said first transistor being directly connected between said supply circuit point and said drive circuit point, said collector-emitter path of said second transistor being connected between said drive circuit point and said reference point; and

input means coupled between said source circuit point and said bases of said first and second transistors for rendering said collector-emitter path of said first transistor conductive and said collector-emitter path of said second transistor non-conductive in response to a first portion of said pulses of said input signal and for rendering said collector-emitter path of said second transistor conductive and said collector-emitter path of said first transistor non-conductive in response to a second portion of said pulses of said input signal.

Th

e present invention relates to drive circuits for infrared remote control transmitters.

e present invention relates to drive circuits for infrared remote control transmitters.Infrared remote control systems for television receivers and the like are known. The chief advantage of infrared remote control systems in comparison to ultrasonic remote control systems is that they are less susceptible to erroneously-generated interference signals. Unfortunately, the human eye may be harmed under conditions of prolonged, continuous and direct exposure to infrared radiation.

In order to reduce the possibility of harm to the eyes of users, infrared remote control systems utilize special pulse codes which minimize the duration of infrared radiation during the transmission of remote controlled messages. However, since in conventional drive circuits for infrared remote control transmitters the infrared light source, e.g., a light-emitting diode or diodes, is typically included in a direct current path from a supply voltage, infrared radiation may be continuously emitted should there be a component failure in the remote control transmitter. Therefore, there is a requirement for drive circuits for use in infrared remote control transmitters in which component failures do not result in the continuous emission of infrared radiation. The present invention concerns such a "fail-safe" drive circuit.

SUMMARY OF THE PRESENT INVENTION

In a remote control transmitter, at least one infrared light-emitting diode is coupled to a point of reference potential and poled so as to be substantially nonconductive in response to voltages having the same polarity as a DC supply voltage for the transmitter and substantially conductive in response to voltages having the polarity opposite to the polarity of the DC supply voltage. Driver means responsive to an input signal is coupled between the source of the DC supply voltage and the light-emitting diode. The driver means normally generates an alternating drive voltage for the light-emitting diode having portions with polarities both the same as and opposite to the polarity of the DC supply voltage. The driver means is arranged so that the portions of the drive signal having the polarity opposite to that of the DC supply voltage are at least inhibited when a component failure occurs.

BRIEF DESCRIPTION OF THE DRAWING

The sole FIGURE of the drawing shows, partially in block diagram form and partially in schematic diagram form, an infrared remote control system constructed in accordance with the present invention as it may be employed in a television receiver arrangement.

DETAILED DESCRIPTION OF THE DRAWING

A tele

vision receiver 1 includes an antenna 3, a tuner 5, an IF signal processing unit 7, a picture signal processing unit 9, a sound signal processing unit 11, a picture tube 13 and a speaker 15 arranged in a conventional fashion to produce visual and audio responses. A power supply 17 is selectively energized to generate DC supply voltages for the portions of the receiver so far described from the AC line voltage in response to an ON/OFF control signal generated by a remote control receiver 19. Receiver 1 also includes a standby power supply 20 which continuously couples a DC supply voltage to remote control receiver 19 so that it is ready to accept messages from a remote control transmitter 21.

vision receiver 1 includes an antenna 3, a tuner 5, an IF signal processing unit 7, a picture signal processing unit 9, a sound signal processing unit 11, a picture tube 13 and a speaker 15 arranged in a conventional fashion to produce visual and audio responses. A power supply 17 is selectively energized to generate DC supply voltages for the portions of the receiver so far described from the AC line voltage in response to an ON/OFF control signal generated by a remote control receiver 19. Receiver 1 also includes a standby power supply 20 which continuously couples a DC supply voltage to remote control receiver 19 so that it is ready to accept messages from a remote control transmitter 21.Remote control receiver 19 includes a photosensitive diode 23. The conduction of photo diode 23 is controlled in response to encoded optical signals having frequencies in the infrared range generated by remote control transmitter 21. A detector 25 senses the changes in the conduction of diode 23 and generates electrical signals corresponding to the encoded optical signals. The electrical signals are decoded by a decoder 27 to generate the ON/OFF control signal for tuning receiver 1 on and off, a CHANNEL SELECTION control signal for controlling the frequency to which a tuner 5 is tuned, and a VOLUME control signal for controlling the sound level of receiver 1.

Remote control transmitter 21 includes a ke

yboard 29 including push buttons (not shown) by which a user may control the various receiver functions enumerated above. When a push button is depressed a corresponding electrical signal is generated by keyboard 29. A pulse encoder 31 is responsive to these electrical signals to generate respective coded pulse signals. The coded pulse signals are processed by a driver 33 to cause infrared light-emitting diodes 35, 37 and 39 to generate corresponding optical signals in the infrared frequency range.

yboard 29 including push buttons (not shown) by which a user may control the various receiver functions enumerated above. When a push button is depressed a corresponding electrical signal is generated by keyboard 29. A pulse encoder 31 is responsive to these electrical signals to generate respective coded pulse signals. The coded pulse signals are processed by a driver 33 to cause infrared light-emitting diodes 35, 37 and 39 to generate corresponding optical signals in the infrared frequency range.Various codes for infrared remote control systems and encoders and decoders for these codes are known. For example, encoder 31 and decoder 27 may comprise S2600 and S2601 integrated circuits manufactured by American Microsystems, Inc. of Santa Clara, Calif.

The exact nature of the codes is not directly germane to the present invention. However, it is desirable for the reasons of safety discussed earlier that the code formats are arranged so that the duration of infrared radiation during a transmission is minimized. Since the pulses of the pulse signals generated by pulse encoder 31 correspond to the intervals of infrared radiation, this may be accomplished by causing the electrical pulse signals generated by encoder 31 to have a relatively low duty cycle, e.g., less than 20 percent. In addition, for safety reasons, it is desirable that light-emitting diodes 35, 37 and 39 be physically separated on transmitter 21 from one another by a distance selected so that the power of the infrared radiation they generate is distributed rather than concentrated in a relatively small area.

While these safety precautions to some extent minimize the danger to users, they do not account for component failures which may cause the continuous, i.e., DC, emission of infrared radiation. Unfortunately, the human eye may be injured when directly exposed to continuous infrared radiation for prolonged periods. While such situations are extremely rare, since they would involve not only a component failure but the misuse of the transmitter, they may occur under extraordinary circumstances. For example, a curious child may point an infrared transmitter with a failed component directly into his eye.

Drive circuit 33 is arranged to prevent the continuous emission of infrared radiation under any for

eseeable component failure mode. Driver 33 includes a push-pull amplifier 41 comprising a PNP transistor 43 and an NPN transistor 45 having their collector-emitter junctions coupled in series between a battery 47 and signal ground. Battery 47 is the source of DC supply voltage for transmitter 21. The output of pulse encoder 31 is coupled to the bases of transistors 43 and 45 through capacitors 49 and 51, respectively. Diodes 53 and 55 are coupled in shunt with the base-emitter junctions of transistors 43 and 45, respectively. The junction of the collectors of transistors 43 and 45 is coupled through parallel connected capacitors 57 and 58 to the cathode of light-emitting diode 35. Light-emitting diodes 35, 37 and 39 are connected in series with the same polarity between capacitors 57 and 58 and signal ground. The polarity of light-emitting diodes 35, 37 and 39 is selected so that they are rendered nonconductive in response to the application of voltages to the cathode of light-emitting diode 35 having the same polarity (i.e., positive) with respect to signal ground as the DC supply voltage provided by battery 47 and only rendered conductive in response to the application of voltages having the opposite polarity (i.e., negative) with respect to signal ground to the DC supply voltage. A diode 59 is connected in shunt with series connected light-emitting diodes 35, 37 and 39 and poled in the opposite direction.

eseeable component failure mode. Driver 33 includes a push-pull amplifier 41 comprising a PNP transistor 43 and an NPN transistor 45 having their collector-emitter junctions coupled in series between a battery 47 and signal ground. Battery 47 is the source of DC supply voltage for transmitter 21. The output of pulse encoder 31 is coupled to the bases of transistors 43 and 45 through capacitors 49 and 51, respectively. Diodes 53 and 55 are coupled in shunt with the base-emitter junctions of transistors 43 and 45, respectively. The junction of the collectors of transistors 43 and 45 is coupled through parallel connected capacitors 57 and 58 to the cathode of light-emitting diode 35. Light-emitting diodes 35, 37 and 39 are connected in series with the same polarity between capacitors 57 and 58 and signal ground. The polarity of light-emitting diodes 35, 37 and 39 is selected so that they are rendered nonconductive in response to the application of voltages to the cathode of light-emitting diode 35 having the same polarity (i.e., positive) with respect to signal ground as the DC supply voltage provided by battery 47 and only rendered conductive in response to the application of voltages having the opposite polarity (i.e., negative) with respect to signal ground to the DC supply voltage. A diode 59 is connected in shunt with series connected light-emitting diodes 35, 37 and 39 and poled in the opposite direction.In operation, pulse encoder 31 generates a pulse signal encoded as described above. The pulse signal includes positive-going pulses. In response to the leading edges of the positive-going pulses, transistor 45 is rendered conductive. In response to the trailing edges of the positive-going pulses, transistor 43 is rendered conductive. Diodes 53 and 55 serve as discharge paths for capacitors 49 and 51 during the intervals when transistors 43 and 45, respectively, are nonconductive. Diodes 53 and 55 also clamp the voltage at the bases of transistors 43 and 45 close to the battery voltage and the voltage at signal ground, respectively, in order to protect the base-emitter junctions of transistors 43 and 45 from reverse breakdown failure voltages. Desirably, capacitors 49 and 51 have relatively small values so that capacitors 49 and 51 are charged and discharged in response to each pulse. As a result, transistors 43 and 45 are alternately rendered conductive and nonconductive in response to each pulse of the pulse signal.

When transistor 43 is conductive (and transistor 45 is nonconductive) capacitors 57 and 58 are charged from battery 47. When transistor 45 is conductive (and transistor 43 is nonconductive) capacitors 57 and 58 are discharged to signal ground. As a result, an alternating drive voltage, i.e., one having polarity excursions above and below the potential at signal ground, are generated at the cathode of light-emitting diode 35. Light-emitting diodes are conductive in response to the negative portions of the drive voltage and are nonconductive in response to the positive portions of the drive voltage. Diodes 35, 37 and 39 only emit infrared radiation when they are conductive. Therefore, infrared radiation is only emitted by transmitter 21 when the drive voltage has a polarity (i.e., negative opposite to the polarity of the DC supply voltage.

Desirably, the capacitance of the combination of capacitors 57 and 58 is relatively large, e.g., 1 microfarad, so that sufficient drive current is provided to light-emitting diodes 35, 37 and 39 to cause them to emit infrared radiation. For the same reason, two capacitors rather than one are used, since the effective series resistance associated with the parallel combination is smaller than the series resistance of a single capacitor.

In the event that there is a component failure within drive circuit 33, drive voltage developed at the cathode of light-emitting diode 35 will be reduced and, in most cases, substantially inhibited. Under these conditions, since the amplitude of the negative portions of the drive signal will at least have a lower than normal amplitude, the infrared radiation will have a lower than normal energy.

Briefly, any failure of a component within driver 33 causing the component to open or short, substantially prevents the development of an alternating drive signal at the cathode of light-emitting diode 35. Since diodes 35, 37 and 39 are rendered conductive only in response to negative-going voltages, no infrared radiation is generated. Any component failure between the extremes of an open or short causes a reduction in the amplitude of the alternating drive signal. By way of example, consider the following failure modes. If either transistor 43 or 45 fails, e.g., by shorting from collector to emitter, capacitors 57 and 58 will be either permanently charged or discharged, thereby preventing the development of an alternating drive signal. If one of capacitors 57 and 58 shorts, only

positive-going voltages are developed at the cathode of light-emitting diode 35. If the collector to emitter junction of transistor 43 and one of capacitors 57 and 58 short, a DC signal is coupled to the cathode of light-emitting diode 35, thereby rendering diode 59 conductive and preventing light-emitting diodes 35, 37 and 39 from being rendered conductive. If diode 59 opens, capacitors 57 and 58 will not be charged thereby preventing the development of an alternating voltage at the cathode of diode 35. If diode 59 fails so as to lose its unidirectional conductive characteristics, i.e., in essence becomes a passive element, an alternating drive signal will be developed but it will have a lower than normal amplitude. Furthermore, failures in pulse encoder 31 causing generation of a DC signal rather than a pulse signal will also cause the loss of an altern

positive-going voltages are developed at the cathode of light-emitting diode 35. If the collector to emitter junction of transistor 43 and one of capacitors 57 and 58 short, a DC signal is coupled to the cathode of light-emitting diode 35, thereby rendering diode 59 conductive and preventing light-emitting diodes 35, 37 and 39 from being rendered conductive. If diode 59 opens, capacitors 57 and 58 will not be charged thereby preventing the development of an alternating voltage at the cathode of diode 35. If diode 59 fails so as to lose its unidirectional conductive characteristics, i.e., in essence becomes a passive element, an alternating drive signal will be developed but it will have a lower than normal amplitude. Furthermore, failures in pulse encoder 31 causing generation of a DC signal rather than a pulse signal will also cause the loss of an altern ating drive signal.

ating drive signal.Driver circuit 33 may be modified in some respects without causing the loss of its "fail-safe" nature. For example, any or all of diodes 53, 55 and 59 may be replaced with resistors. While this modification causes a reduction in efficiency of the normal operation of drive circuit 33, it does not alter its "fail-safe" nature. These and other modifications are intended to be within the scope of the present invention as set forth in the following claims.

TELEFUNKEN CHASSIS 712A Tuning circuit arrangement

A tuning circuit arrangement comprises one or more tuned circuits whose frequency range is tuned by tuning diodes, means being provided for varying the tuning voltage of the tuning diodes to provide exclusive variation of the tuned circuit capacitance of the tuned circuit.

1. A circuit for adjusting a tuning circuit, the tuning circuit including at least one resonant circuit composed of a variable inductance and a variable capacitance constituted by at least one voltage-variable tuning diode, one side of the resonant circuit being connected to a point at circuit ground potential and adjustment of the resonant circuit being effected by changing the resonant circuit inductance and the resonant circuit capacitance, with changing of the resonant circuit capacitance being effected exclusively by varying the tuning voltage of the tuning diode, the tuning circuit further including a source of a variable tuning potential which is variable over a range between maximum and minimum extreme values, each extreme value being different from the circuit ground potential, and said circuit for adjusting comprising at least one adjustment potentiometer connected between a point of said source providing the variable tuning potential and a point of said source permanently providing one of said extreme values, said potentiometer having an adjustable tap connected to provide the tuning voltage for said tuning diode. 2. An arrangement as defined in claim 1 wherein said tuning circuit includes a plurality of said resonant circuits and said circuit for adjusting comprises a plurality of said potentiometers connected together in parallel and each having a respective adjustable tap connected to provide the tuning voltage for at least one respective tuning diode. 3. An arrangement as defined in claim 1 wherein said source comprises a tuning potentiometer connected to have a respective one of the extreme values of the tuning potential at each of its ends and having an adjustable tap providing the variable tuning potential, and said adjustment potentiometer is connected between one end and said movable tap of said tuning potentiometer. 4. An arrangement as defined in claim 1 wherein said tuning circuit includes at least two of said resonant circuits and said adjustable tap of said adjustment potentiometer is connected to provide the tuning voltage for said at least two resonant circuits. 5. An arrangement as defined in claim 4 wherein said resonant circuits have respectively different relative frequency variations.

1. A circuit for adjusting a tuning circuit, the tuning circuit including at least one resonant circuit composed of a variable inductance and a variable capacitance constituted by at least one voltage-variable tuning diode, one side of the resonant circuit being connected to a point at circuit ground potential and adjustment of the resonant circuit being effected by changing the resonant circuit inductance and the resonant circuit capacitance, with changing of the resonant circuit capacitance being effected exclusively by varying the tuning voltage of the tuning diode, the tuning circuit further including a source of a variable tuning potential which is variable over a range between maximum and minimum extreme values, each extreme value being different from the circuit ground potential, and said circuit for adjusting comprising at least one adjustment potentiometer connected between a point of said source providing the variable tuning potential and a point of said source permanently providing one of said extreme values, said potentiometer having an adjustable tap connected to provide the tuning voltage for said tuning diode. 2. An arrangement as defined in claim 1 wherein said tuning circuit includes a plurality of said resonant circuits and said circuit for adjusting comprises a plurality of said potentiometers connected together in parallel and each having a respective adjustable tap connected to provide the tuning voltage for at least one respective tuning diode. 3. An arrangement as defined in claim 1 wherein said source comprises a tuning potentiometer connected to have a respective one of the extreme values of the tuning potential at each of its ends and having an adjustable tap providing the variable tuning potential, and said adjustment potentiometer is connected between one end and said movable tap of said tuning potentiometer. 4. An arrangement as defined in claim 1 wherein said tuning circuit includes at least two of said resonant circuits and said adjustable tap of said adjustment potentiometer is connected to provide the tuning voltage for said at least two resonant circuits. 5. An arrangement as defined in claim 4 wherein said resonant circuits have respectively different relative frequency variations. The invention relates to a tuning circuit arrangement comprising one or more tuning circuits in which tuning diodes are provided for tuning of the frequency range. In such an arrangement, the adjustment of the tuned circuit takes place, for example, by changing the tuned circuit inductance and the tuned circuit capacitance.

As is known, tuning circuits have the object of tuning the resonant circuits of selective amplifiers and/or oscillators to a given resonant frequency. In a known tuning circuit, the adjustment to synchronous operation in each circuit takes place via a tuning coil and a particular trimmer capacitor. In the known tuning circuit arrangement a multiply repeated adjustment of the inductance and the capacitance is required for adjustment to synchronous operation, because the setting of the trimmer capacitors again changes the resonant frequency of the frequency previously set inductively.

SUMMARY OF THE INVENTION

It

is an object of the invention to provide a tuning circuit arrangement with simplified adjustment.

is an object of the invention to provide a tuning circuit arrangement with simplified adjustment.According to a first aspect of the invention, there is provided a tuning circuit arrangement comprising one or more tuned circuits, tuning diodes in said tuned circuits for tuning the frequency range of said tuned circuits and means for varying the tuning voltage of said tuning diodes for providing exclusive variation of the tuned circuit capacitance of said tuned circuit.

According to a second aspect of the invention, there is provided a tuning circuit arrangement comprising one or more tuning circuits, in which tuning diodes are provided for the purpose of tuning the frequency range and in which the tuned circuit adjustment takes place by changing the tuned circuit inductance and the tuned circuit capacitance, characterized in that the adjustment in capacitance takes place exclusively by varying the tuning voltage for the tuning diode(s).

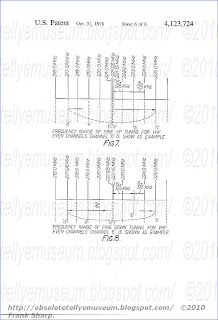

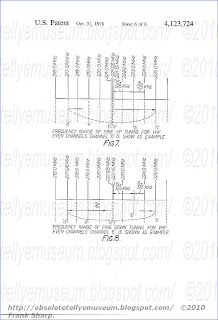

BRIEF DESCRIPTION OF THE DRAWINGS

The invention will now be described in greater detail, by way of example, with reference to the drawings in which:

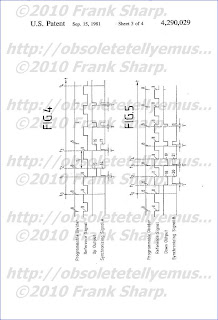

FIG. 1 is a circuit diagram showing a first form of circuit arrangement in accordance with the invention as applied to two resonant circuits;

FIG. 2 is a circuit diagram similar to FIG. 1 but showing the arrangement applied to n resonant circuits;

FIG. 3 is a circuit diagram similar to FIG. 1 but showing the arrangement with a different form of adjustment;

FIG. 4 is a circuit diagram similar to FIG. 2 in which the arrangement of FIG. 3 is applied to n resonant circuits;

FIG. 5 is a circuit diagram showing a part of the arrangement showing a different form of adjusting circuitry;

FIG. 6 is a circuit diagram similar to FIG. 5 but showing a still further form of adjusting circuitry;

FIG. 7 is a block diagram of part of the arrangement provided with temperature compensation and,

FIG. 8 is a block diagram similar to FIG. 7 but including a decoupling circuit.

DESCRIPTION OF THE PREFERRED EMBODIMENTS

In a tuning circuit arrangement of the type mentioned at the beginning it is proposed in accord

ance with the invention and in order to solve the object that the adjustment in capacitance should take place exclusively by variation of the tuning voltage for the tuning diode(s).

ance with the invention and in order to solve the object that the adjustment in capacitance should take place exclusively by variation of the tuning voltage for the tuning diode(s).The essence of the invention on the one hand consists in that special trimmer capacitors for achieving an adjustment in capacitance are omitted and that the adjustment in capacitance takes place exclusively by variations of the tuning voltage for the tuning diode(s) which is in contrast to the known method, and does not take place by means of trimmer capacitors. On the other hand, the invention does not require any repetitive adjustment of the tuned circuits of the tuning circuits.

The tuning circuit arrangement in accordance with the invention makes it possible to reduce considerably the required maximum tuning voltage. With the tuning circuit arrangement in accordance with the invention it is possible to operate with small tuning voltages even when using tuning diodes having abrupt pn junction. The sought after simplification of the adjustment can be achieved by means of the fact that the capacitative adjustment does not influence the previously operated adjustment in inductance.

In the tuning circuit arrangement according to the invention potentiometers, for example, are provided in order to adjust the capacitance. There is the possibility of using the same adjusting means for adjusting the capacitance of two or more tuned circuits. Similarly, the same adjustment means may serve to adjust the capacitance of several tuned circuits having varying relative frequency variation.

In accordance with a further refinement of the invention a circuit arrangement for producing minimum and maximum tuning potentials is provided which is constructed so that the potentials produced by it have such a temperature dependence that the effect of temperature on the tuning circuit is compensated.

It is advisable to connect a decoupling circuit between the means for adjusting capacitance and the 6 tuning potentiometers, the decoupling circuit reducing the electrical load on the tuning potentiometer through the adjustment means. In accordance with an embodiment of the invention, precautions are taken to ensure that one of the two potentials applied to an adjustment potentiometer, does not change during adjustment.

The adjustment potentiometer or potentiometers are connected for example between a point in the circuit at which the variable tuning potential is available and a point in the circuit at which the minimum tuning potential is available. There is also the possibility of connecting the adjustment potentiometer or potentiometers between a point in the circuit at which the variable tuning potential is available and a point in the circuit at which the maximum tuning potential is available.

Referring now to the drawings, FIG. 1 shows an electronic tuning circuit in accordance with the inv

ention which operates with tuning diodes. The tuning circuit of FIG. 1, which is for example a component of a VHF tuner, consists of two variable-frequency resonant circuits and in fact an oscillator circuit 1 and a resonant circuit 2 for selecting the input signal. The oscillator circuit comprises an inductance 3 and a tuning diode 4, which is a double diode in this embodiment. The resonant circuit 2 comprises an inductance 5 and a tuning diode 6, which in this embodiment is also a double diode. As may be seen from FIG. 1, neither of the two resonant circuits 1 and 2 has a trimmer capacitor. Of course, parallel to the resonant circuits there are unavoidable circuit capacitances 7 and 8 which are shown in broken lines.

ention which operates with tuning diodes. The tuning circuit of FIG. 1, which is for example a component of a VHF tuner, consists of two variable-frequency resonant circuits and in fact an oscillator circuit 1 and a resonant circuit 2 for selecting the input signal. The oscillator circuit comprises an inductance 3 and a tuning diode 4, which is a double diode in this embodiment. The resonant circuit 2 comprises an inductance 5 and a tuning diode 6, which in this embodiment is also a double diode. As may be seen from FIG. 1, neither of the two resonant circuits 1 and 2 has a trimmer capacitor. Of course, parallel to the resonant circuits there are unavoidable circuit capacitances 7 and 8 which are shown in broken lines.The two resonant circuits 1 and 2 must be adjusted to achieve synchronous operation. In accordance with the invention the adjustment potentiometers 9 and 10 are provided for this purpose. The adjustment potentiometers 9 and 10 are connected in parallel with one another in the embodiment of FIG. 1. Two limiting potentials are required for the tuning circuit; in fact the largest potential U max at point 11 and the smallest potential U min at point 12. In the embodiment of FIG. 1 the two adjustment potentiometers 9 and 10 lie between the wiper contact 13 of the tuning potentiometer 14 and the point 12 having the potential U min . The tuning potentiometer 14 lies between the points 11 and 12, i.e. between the maximum potential U max and the minimum potential U min . The maximum tuning potential U max and the minimum tuning potential U min are in fact linked together, yet they are produced in a separate circuit arrangement. This is indicated symbolically in FIG. 1 by means of the two voltage sources 23 and 24. The minimum tuning potential U min is therefore not derived via a purely ohmic voltage divider from the maximum tuning potential U max .

In the tuning circuit of FIG. 1, in the case where the tuning potentiometer 14 is set to the minimum tuning voltage, the voltages taken from the adjustment potentiometers 9 and 10 are not influenced by the settings of the adjustment potentiometer. Therefore, if the wiper contact 13 of the tuning potentiometer 14 is located at the lowest position then no matter how the adjustment potentiometers 9 and 10 are rotated the adjustment voltages for the tuning diodes will not be influenced by this. This has the consequence that setting in the upper frequency range has no influence on the previously set lower frequency. The adjustment of the lower frequency is only dependent on the inductance adjustment of the inductances 3 and 5.

The tuning circuit of FIG. 2 is distinguished from the tuning circuit of FIG. 1 by the fact that instead of only two resonant circuits n resonant circuits are provided and, instead of only two adjustment potentiometers, m adjustment potentiometers are provided. m may be smaller than n if not merely one resonant circuit but more than one resonant circuit is adjusted by means of a single adjustment potentiometer.

The tuning circuit of FIG. 2 is distinguished from the tuning circuit of FIG. 1 by the fact that instead of only two resonant circuits n resonant circuits are provided and, instead of only two adjustment potentiometers, m adjustment potentiometers are provided. m may be smaller than n if not merely one resonant circuit but more than one resonant circuit is adjusted by means of a single adjustment potentiometer.FIG. 3 shows an embodiment of the invention in which in contrast to FIGS. 1 and 2 the adjustment potentiometers 9 and 10 lie between the wiper contact 13 of the tuning potentiometer 14 and point 11 having the potential U max . In this case, the adjustment in inductance takes place in the upper frequency and the adjustment in capacitance takes place in the lower frequency by means of the adjustment potentiometers 9 and 10.

The tuning circuit of FIG. 4 is distinguished from the tuning circuit of FIG. 3 by the fact that, instead of only two resonant circuits, again n resonant circuits are provided and instead of only two adjustment potentiometers m adjustment potentiometers are provided.

According to FIG. 5 the adjustment in capacitance is undertaken for the upper frequency by setting the maximum tuning potential. While in the tuning circuits of FIGS. 1 to 4 the adjustment of the individual tuned circuits is independent, in the arrangement of FIG. 5 the setting of the maximum tuning potential effects all tuned circuits. The setting of the maximum tuning potential takes place in the arrangement of FIG. 5 by means of the voltage source 20. The voltage supplying the tuning diodes may for example be taken from the wiper contact 13 of the tuning potentiometer 14, from a fixed voltage divider 21 or from the wiper contact of the adjustment potentiometer 9. Several adjustment potentiometers may be provided instead of only one adjustment potentiometer.

The arrangement of FIG. 6 is distinguished from the arrangement of FIG. 5 by the fact that the minimum tuning potential is made settable instead of the maximum tuning potential for the purpose of adjustment. Moreover, in the arrangement of FIG. 6, the network which comprises the voltage divider 21 and the adjustment potentiometer 9, is connected between the wiper contact 13 of the adjustment potentiometer 14 and the maximum tuning potential 11.

According to FIG. 7, the maximum and minimum tuning potential is produced by means of a circuit arrangement 15 which has the object of supplying such a temperature effect of the potential that the temperature effect of the tuning circuit is compensated by an appropriate temperature effect of the potentials.

The arrangement 16 of FIG. 8 also produces the minimum and maximum tuning potentials at the points 11 and 12 as well as the effective temperature on these potentials which is required for temperature compensation of the tuning circuit. In addition, the arrangement 16 contains a decoupling circuit which lies between the wiper contact 13 of the tuning potentiometer 14 and the adjustment potentiometers 9 and 10.

The tuning circuit dealt with in the embodiments is developed for positive tuning potentials. In a similar manner, the tuning circuits of the invention may also be designed for negative tuning potentials.

It will be understood that the above description of the present invention is susceptible to various modification changes and adaptations.

TELEFUNKEN PALCOLOR 8848J QUARTZ MEMORY CHASSIS 712A DPS2 TELEFUNKEN PLL SYNTHESIZER PLESSEY CHIPSET CT1112 CT1111 Digital phase control circuit including an auxiliary circuit:

This application describes a receiver in which channel selection is controlled by a frequency synthesizer a sweep of available channels is made by a channel selecting arrangement and this sweep is arranged to be stopped when a signal is received. When the sweeping is stopped a fine tuning arrangement takes control to respond to the frequency of the received signal and to compensate for any drift of that signal. A tuning circuit for a high frequency receiver in which the received frequency is determined by a voltage-controlled oscillator, the present tuning frequency is indicated by a counter connected to the oscillator and producing a representation of each digit of the decimal number identifying the current received frequency, representations of the digits of the number identifying the desired received frequency are fed in via a rotary switch , and the decimal number representations are compared in a comparator to produce a control voltage that brings the oscillator frequency to the desired value, and in which the comparator is capable of comparing only one digit of the number representations at a time and receives the digits of corresponding significance in sequence, starting with the most significant digit, and the rate at which the control voltage is varied is made inversely proportional to the number of changes in the direction of the inequality of the digits of one of the number representations being compared relative to the corresponding digits of the other number representation being compared.

1. In a tuning circuit for a high frequency receiver, which circuit includes a voltage controllable superheterodyne oscillator arranged to receive a control voltage and to produce an oscillation whose frequency is determined by the value of the control voltage and determines the broadcast frequency to which the receiver is tuned, a counter connected to sense the frequency of the oscillations being generated by the oscillator and to produce therefrom a count state in the form of representations of the digits of a first decimal number identifying the broadcast frequency to which the receiver is currently tuned, input means for generating representations of the digits of a second decimal number identifying the broadcast frequency to which it is desired to tune the receiver, and a comparison circuit for comparing the decimal number representations being produced by the counter and the input means in order to vary the control voltage in a direction to cau

2. An arrangement as defined in claim 1 wherein said adjustment means comprises a sequence counter connected for counting the number of such sequences and having its count state set to zero at the beginning of each tuning operation.

3. An arrangement as defined in claim 2 wherein said adjustment means further comprises a logic gate connected to the output of said sequence counter and having a number of outputs equal to a selected number of desired control voltage variation rates, said gate being arranged to provide a certain logic potential at one of its outputs in dependence on the count state of said sequence counter.

4. An arrangement as defined in claim 3 wherein said comparison circuit includes an amplifier arranged to provide an output signal which effects variation of the control voltage, and said adjustment means further comprise a plurality of resistors having respectively different resistance values and each connected between a respective output of said gate and said amplifier for causing the control voltage variation rate to have a value determined by the resistance value of that resistor whose associated gate output is providing the certain logic potential.

5. An arrangement as defined in claim 4 wherein the comparison circuit further includes a capacitor connected to receive the output signal from said amplifier so that the voltage thereacross constitutes the control voltage, said amplifier being arranged for supplying said capacitor with a charging or discharging current proportional to the current flowing through that one of said resistors whose associated gate output is providing the certain logic potential.

5. An arrangement as defined in claim 4 wherein the comparison circuit further includes a capacitor connected to receive the output signal from said amplifier so that the voltage thereacross constitutes the control voltage, said amplifier being arranged for supplying said capacitor with a charging or discharging current proportional to the current flowing through that one of said resistors whose associated gate output is providing the certain logic potential. 6. An arrangement as defined in claim 4 wherein said amplifier is connected to said second and third comparator outputs for causing the direction of variation of the control voltage to be determined on the basis of which one of said second and third comparator outputs is providing a signal.

7. An arrangement as defined in claim 4 wherein said gate is arranged to cause its outputs to be blocked at a selected maximum count state of said sequence counter for preventing current flow through any of said resistors.

8. An arrangement as defined in claim 4 wherein said logic gate is arranged to have its outputs blocked when there is coincidence between all digits of the two numbers.

9. An arrangement as defined in claim 2 wherein said adjustment means comprises a programmable frequency divider connected to have its dividing ratio determined by the counter state of said sequence counter in a manner such that the dividing ratio increases with increasing counter state.

10. An arrangement as defined in claim 9 wherein said adjustment means further comprises means for producing square wave oscillations of a constant frequency connected to feed such oscillations to said divider.

11. An arrangement as defined in claim 10 wherein said adjustment means comprises a digital-analog converter connected to the output of said divider and providing an output voltage whose value determines the magnitude of the rate of variation of the control voltage.

The present invention relates to a tuning circuit for a high frequency receiver having a superheterodyne oscillator whose frequency can be varied by means of a tuning voltage in order to tune the receiver to a desired station.

In such circuits, the tuning voltage, which is a direct voltage, is generated by a comparison circuit which effects a comparison between two numbers. The first number identifies the counter state of a counting device which periodically counts the oscillations of the superheterodyne oscillator on the basis of the intermediate frequency. This number thus constitutes the received frequency, or possibly the received channel or station. The second number is fed to the comparison circuit via an input keyboard provided with a series-connected coder and identifies the desired channel or station to which the receiver is to be tuned. The comparison circuit has three outputs, one output for the c

omparison result "equality" and one each for the two non-equality results "greater" and "less".

omparison result "equality" and one each for the two non-equality results "greater" and "less". In the circuit disclosed in U.S. application Ser. No. 708,754, filed by the present applicant and Dieter Rottmann and Stephan Wuttke on July 26, 1976, the comparison is effected by a multiplex operation and the comparison circuit is composed of only a single comparator which can effect a comparison with respect to only one digit, or level of significance, of the numbers at a time. This comparator receives, in succession, the representations of the digits of the two numbers to be compared, beginning with the most significant digit.

If in the described tuning circuit the two numbers are unequal, the tuning circuit, and thus the frequency of the superheterodyne oscillator, is changed until the frequency identified by the number fed in has been attained. The rate at which the tuning voltage changes is relatively great if the two numbers to be compared differ from one another in all digit positions. The rate of change becomes less as more digits of the two numbers, beginning with the most significant digit, become equal. When all digits are equal, the frequency will no longer be changed. The tuning rate thus decreases as more digits become identical, this result being a function of the evaluation circuit provided in the above-cited application. The successive rates there are proportional to 1/2 . . . 1/n, where n = number of digit positions, e.g. 5. It has been found that this tuning process takes a relatively long time, which many operators consider to be a drawback.

SUMMARY OF THE INVENTION

It is therefore an object of the present invention to shorten the time required for the tuning process.

These and other objects are achieved, in a tuning circuit for a high frequency receiver, which circuit includes a voltage controllable superheterodyne oscillator arranged to receive a control voltage and to produce an oscillation whose frequency is determined by the value of the control voltage and determines the broadcast frequency to w

hich the receiver is tuned, a counter connected to sense the frequency of the oscillations being generated by the oscillator and to produce therefrom a count state in the form of representations of the digits of a first decimal number identifying the broadcast frequency to which the receiver is currently tuned, input means for generating representations of the digits of a second decimal number identifying the broadcast frequency to which it is desired to tune the receiver, and a comparison circuit for comparing the decimal number representations being produced by the counter and the input means in order to vary the control voltage in a direction to cause those two number representations to coincide, the comparison circuit including a comparator capable of comparing the representations of one digit of each of two numbers and having two inputs connected, respectively, to the counter and to the input means, the comparator being arranged to receive, at one of its inputs, each digit representation produced by the counter, starting with the most significant digit, and, at the other of its inputs, simultaneously therewith each digit representation of corresponding significance generated by the input means, the comparator including a first output providing a signal when the digit representations at its inputs are identical, a second output providing a signal when the digit representation at its one input represents a value larger than that of the digit representation at its other input, and a third output providing a signal when the digit representation at its one input represents a value smaller than that of the digit representation at its other input, by the provision of tuning voltage adjustment means connected to the comparator outputs and responsive to the number of sequences of termination of a signal at one of the second and third outputs and subsequent initiation of a signal at the other of the second and third outputs for varying the control voltage at a rate inversely proportional to such number of sequences.

hich the receiver is tuned, a counter connected to sense the frequency of the oscillations being generated by the oscillator and to produce therefrom a count state in the form of representations of the digits of a first decimal number identifying the broadcast frequency to which the receiver is currently tuned, input means for generating representations of the digits of a second decimal number identifying the broadcast frequency to which it is desired to tune the receiver, and a comparison circuit for comparing the decimal number representations being produced by the counter and the input means in order to vary the control voltage in a direction to cause those two number representations to coincide, the comparison circuit including a comparator capable of comparing the representations of one digit of each of two numbers and having two inputs connected, respectively, to the counter and to the input means, the comparator being arranged to receive, at one of its inputs, each digit representation produced by the counter, starting with the most significant digit, and, at the other of its inputs, simultaneously therewith each digit representation of corresponding significance generated by the input means, the comparator including a first output providing a signal when the digit representations at its inputs are identical, a second output providing a signal when the digit representation at its one input represents a value larger than that of the digit representation at its other input, and a third output providing a signal when the digit representation at its one input represents a value smaller than that of the digit representation at its other input, by the provision of tuning voltage adjustment means connected to the comparator outputs and responsive to the number of sequences of termination of a signal at one of the second and third outputs and subsequent initiation of a signal at the other of the second and third outputs for varying the control voltage at a rate inversely proportional to such number of sequences. Thus, in the present invention, the number of reversals of the inequality results determines the respective level of the rate of change of the tuning voltage. The greater the number of changes in inequality results, i.e. the smaller the difference between the two numbers, the lower will be the tuning rate.

In the tuning circuit described in the above-cited earlier U.S. application, there is also a reduction in the tuning rate as a result of different stages of the rate of change, but the differences between the various stages are only slight. The reason for this is that the tuning voltage which effects a change in frequency is generated by means of an integrating member, or low-pass filter, from pulses which vary in repetition rate by a maximum of, for example, 1:5 per unit time, corresponding to the number of digit positions. The direct voltage at the output of the integrating member can therefore only take on values which correspond to a linear graduation 0, 1, 2, . . . n.

In the present invention, however, it is possible to provide practically any difference between the stages, or graduated variations, in the rate of change so that the tuning process can be optimized.

The periodical "Funkschau" 1974, Issue No. 3, at page 93, discloses a circuit which assigns different significances to individual decades during the comparison of two numbers associated with generation of the tuning voltage. However, this comparison of the two numbers is not performed in a multiplex operation but in a parallel operation. Therefore each decade must have its own comparator, causing the known tuning circuit to be very expensive.

1. A receiver comprising a frequency synthesizer controlled channel selection means which includes a controllable oscillator having a frequency and providing an output signal, dividing means including a

n adjustable divider for dividing the output signal to obtain a divided output signal, a reference signal source for providing a reference signal, a comparator for comparing the reference signal with the divided output signal and for providing a control signal to control the controllable oscillator, fine tuning means for fine tuning the frequency of the controllable oscillator, means for initiating a sweep of available channels by the channel selection means, means for stopping the sweep on reception of a signal by said receiver on one of the available channels, and control means operable on cessation of sweeping and responsive to the frequency of the signal for controlling the fine tuning means to compensate for frequency drift of the signal. 2. A receiver as claimed in claim 1 wherein the receiver is a television receiver. 3. A receiver as claimed in any one of claims 1 or 2 wherein the control means comprises level detector means for receiving a frequency representative signal having a level which is representative of the frequency of the received signal so as to monitor frequency drift of said received signal, and for providing an output signal when a predetermined frequency drift is detected. 4. A receiver as claimed in claim 3 wherein two level comparators are provided, each of said two level comparators receiving the frequency representative signal and a respective reference level and providing an output representative of an upward and downward frequency drift, respectively, exceeding predetermined limits. 5. A receiver as claimed in claim 4 wherein the frequency representative signal is provided by automatic frequency control (A.F.C.) means for automatically controlling the frequency of the received signal. 6. A receiver as claimed in claim 5 wherein the automatic frequency control means comprises an A.F.C. discriminator. 7. A receiver as claimed in claim 3 wherein the frequency representative signal is provided by automatic frequency control (A.F.C.) means for automatically controlling the frequency of the received signal. 8. A receiver as claimed in claim 3 wherein the control means controls the fine tuning means via a signal path which includes blocking means for blocking said signal path until said signal is received. 9. A receiver as claimed in claim 3 wherein said channel selection means has a control input, and the means for initiating the sweep comprises an operator control coupled to the control input of the channel selection means, and the means for stopping the sweep is operative to isolate the operator control from the control input of the channel selection means. 10. A receiver as claimed in claim 3 wherein the means for stopping the sweep includes detecting means for detecting the reception of said signal. 11. A receiver as claimed in claim 10 wherein the detecting means comprises a synch comparator operative to compare video signals with line flyback signals and to provide an output signal having a level indicative of the reception of said signal. 12. A receiver as claimed in claim 1 wherein the control means controls the fine tuning means via a signal path which includes blocking means for blocking said signal path until said signal is received. 13. A receiver as claimed in claim 12 wherein the blocking means comprises gate means connected to said signal path and receiving, as a second input, a reception signal indicative of the reception of said signal. 14. A receiver as claimed in claim 1 wherein said channel selection means has a control input, and the means for initiating the sweep comprises an operator control coupled to the control input of the channel selection means, and the means for stopping the sweep is operative to isolate the operator control from the control input of the channel selector means. 15. A receiver as claimed in claim 14 wherein the operator control is coupled to the channel selection means via gating means operative for opening on operation of the operator control. 16. A receiver as claimed in claim 15 wherein the means for stopping the sweep is arranged to provide a blocking signal operative to block the gating means on receipt of said signal. 17. A receiver as claimed in claim 1 wherein the means for stopping the sweep includes detecting means for detecting the reception of said signal. 18. A receiver as claimed in any one of claims 2 or 17 wherein the detecting means comprises a synch comparator operative to compare video signals with line flyback signals and to provide an output signal having a level indicative of the reception of said signal.

n adjustable divider for dividing the output signal to obtain a divided output signal, a reference signal source for providing a reference signal, a comparator for comparing the reference signal with the divided output signal and for providing a control signal to control the controllable oscillator, fine tuning means for fine tuning the frequency of the controllable oscillator, means for initiating a sweep of available channels by the channel selection means, means for stopping the sweep on reception of a signal by said receiver on one of the available channels, and control means operable on cessation of sweeping and responsive to the frequency of the signal for controlling the fine tuning means to compensate for frequency drift of the signal. 2. A receiver as claimed in claim 1 wherein the receiver is a television receiver. 3. A receiver as claimed in any one of claims 1 or 2 wherein the control means comprises level detector means for receiving a frequency representative signal having a level which is representative of the frequency of the received signal so as to monitor frequency drift of said received signal, and for providing an output signal when a predetermined frequency drift is detected. 4. A receiver as claimed in claim 3 wherein two level comparators are provided, each of said two level comparators receiving the frequency representative signal and a respective reference level and providing an output representative of an upward and downward frequency drift, respectively, exceeding predetermined limits. 5. A receiver as claimed in claim 4 wherein the frequency representative signal is provided by automatic frequency control (A.F.C.) means for automatically controlling the frequency of the received signal. 6. A receiver as claimed in claim 5 wherein the automatic frequency control means comprises an A.F.C. discriminator. 7. A receiver as claimed in claim 3 wherein the frequency representative signal is provided by automatic frequency control (A.F.C.) means for automatically controlling the frequency of the received signal. 8. A receiver as claimed in claim 3 wherein the control means controls the fine tuning means via a signal path which includes blocking means for blocking said signal path until said signal is received. 9. A receiver as claimed in claim 3 wherein said channel selection means has a control input, and the means for initiating the sweep comprises an operator control coupled to the control input of the channel selection means, and the means for stopping the sweep is operative to isolate the operator control from the control input of the channel selection means. 10. A receiver as claimed in claim 3 wherein the means for stopping the sweep includes detecting means for detecting the reception of said signal. 11. A receiver as claimed in claim 10 wherein the detecting means comprises a synch comparator operative to compare video signals with line flyback signals and to provide an output signal having a level indicative of the reception of said signal. 12. A receiver as claimed in claim 1 wherein the control means controls the fine tuning means via a signal path which includes blocking means for blocking said signal path until said signal is received. 13. A receiver as claimed in claim 12 wherein the blocking means comprises gate means connected to said signal path and receiving, as a second input, a reception signal indicative of the reception of said signal. 14. A receiver as claimed in claim 1 wherein said channel selection means has a control input, and the means for initiating the sweep comprises an operator control coupled to the control input of the channel selection means, and the means for stopping the sweep is operative to isolate the operator control from the control input of the channel selector means. 15. A receiver as claimed in claim 14 wherein the operator control is coupled to the channel selection means via gating means operative for opening on operation of the operator control. 16. A receiver as claimed in claim 15 wherein the means for stopping the sweep is arranged to provide a blocking signal operative to block the gating means on receipt of said signal. 17. A receiver as claimed in claim 1 wherein the means for stopping the sweep includes detecting means for detecting the reception of said signal. 18. A receiver as claimed in any one of claims 2 or 17 wherein the detecting means comprises a synch comparator operative to compare video signals with line flyback signals and to provide an output signal having a level indicative of the reception of said signal. In our co-pending G.B. patent application No. 32419/16 corresponding to U.S. Pat. No. 4,123,724 of Das et al, issued on Oct. 31, 1978, there is described a frequency synthesizer control arrangement suitable for use in a television receiver for effecting frequency control of its local oscillator for the purpose of channel selection.

In that application two methods of channel selection have been described. The first method is to select the channel number in a digital switch and then to enter the channel numbers by pressing the TUNE control.

The second method is to effect a sweep through the whole range of channel numbers until a required number is reached. In both methods fine tuning is effected by operation of the provided fine tune controls.

In the channel sweep tuning method disclosed, a user has to keep the tuning control operated until the required channel is reached at which point the control must be immediately released. This can be a disadvantage if the user is not familiar with the channel numbers of his area, he must watch the T.V. screen and release the control at the moment a picture appears.

This invention seeks to provide a receiver arrangement employing frequency synthesizer controlled channel selection in which the above mentioned disadvantage is mitigated.

According to this invention there is provided a receiver comprising frequency synthesizer controlled channel selection means which includes a fine tuning arrangement; means for initiating a sweep of available channels by the channel selection means; means for stopping the sweep on reception of a signal and means, operable on cessation of sweeping and responsive to the frequency of the signal, and arranged to control the fine tuning arrangement to compensate for frequency drift of the signal.

The receiver may be in the form of a television receiver.

The means operable a cessation of sweeping may comprise level detector means arranged to receive a signal whose level is representative of the frequency of the received signal and to provide an output signal when a predetermined frequency drift is detected.

The means operable a cessation of sweeping may comprise level detector means arranged to receive a signal whose level is representative of the frequency of the received signal and to provide an output signal when a predetermined frequency drift is detected.In a preferred form two level comparators are provided each arranged to receive the frequency representative signal and a respective reference level and to provide an output respectively representative of an upward and downward frequency drift exceeding predetermined limits.

The signal whose level is representative of the frequency of the received signal may be provided by automatic frequency control (A.F.C.) means conveniently in the form of an A.F.C. discriminator.

The means operable or cessation of sweeping may be arranged to control the fine tuning arrangement via a signal path which includes means for blocking said signal path until the said signal is received.

The means for blocking may be in the form of gate means connected to the said signal path and arranged to receive a second input a signal indicative of the receipt of the said signal.

The means for initiating a sweep may comprise an operator control coupled to control input means of the channel selection means, and the means for stopping sweeping is operative to isolate the operator control from the said control input means.

The operator may be coupled to the channel selection means via gating means operative to open an operation of the operator control and the means for stopping sweeping may provide a signal operative to block the gating means or receipt of the said signal.

The means for stopping sweeping may include means for detecting the reception of the said signal which in a preferred form of television receiver comprises a sync comparator operative to compare video signals with line flyback signals and to provide an output signal whose level is indicitive of the reception of the said signal.

The invention will now be further described with reference to the accompanying single FIGURE drawing which shows schema

tically a television receiver in accordance with the invention.

tically a television receiver in accordance with the invention. Referring to the drawings there is shown a television receiver which has a local oscillator and other standard television components such as i.f. amplifier and sound and vision detection and reproduction circuits, all shown within rectangular box referenced 1. A frequency synthesizer unit 2 controls the frequency of the local oscillator in order to provide channel selection.

The frequency synthesizer unit 2 has a fine tuning arrangement and may conveniently be as described in our co-pending application No. 32419/76 corresponding to U.S. Pat. No. 4,123,724 of Das et al, issued on Oct. 31, 1978,.

The frequency synthesizer unit 2 is capable of effecting a sweep of available channels and has three inputs which correspond to inputs to the synthesizer described in the co-pending application. A first input 3 is a channel sweep/fine tuning input and when an appropriate signal level is applied to this input the frequency synthesizing unit 2 is caused to sweep through available reception channels. In the absence of a suitable signal level to the input 3 the frequency synthesizer unit 2 is only operative in the fine tune mode in a manner to be described.

The second and third inputs 4 and 5 are respectively up and down control inputs. The up and down control inputs 4 and 5 perform a dual function of indicating to the frequency synthesizer unit 2 during channel sweeping the direction in which sweeping is to be effective and also act as fine tuning signal inputs when the synthesizer is operating in the fine tuning mode.

To initiate sweeping two operator controls are provided in the form of push button switches 6 and 7 the switch 6 being a sweep up switch while the switch 7 is a sweep down switch. The switches 6 and 7 are operative to connect potentials applied at terminals 8 and 9 respectively to the SET input of flip-flops 10 and 11 respectively. The terminal 8 connected via the switch 6 to the SET input of the flip-flop 10 is also connected via the switch to the RESET input of the flip-flop 11 whilst the terminal 9 is similarily connected to the RESET input of the flip-flop 10 so that whenever one of the two flip-flops is SET the other is automatically RESET. Typically potentials of 5 volts are applied to the terminals 8 and 9.

The flip-flops 10 and 11 have Q outputs respectively connected to one input of NOR gates 12 and 13 which have outputs c

onnected via one position of respective two position auto/manual switches 14 and 15 the wipers of which are connected to respective inputs of an OR gate 16 whose output is connected to the channel sweep/fine tuning input 3 of the frequency synthesizer unit 2. The wiper of the switch 14 is also connected to one input of an OR gate 17 whose output is connected to the input 4 of the synthesizer unit 2 whilst the wiper of the switch 15 is connected to one input of an OR gate 18 whose output is connected to the input 5 of the synthesizer unit 2.

onnected via one position of respective two position auto/manual switches 14 and 15 the wipers of which are connected to respective inputs of an OR gate 16 whose output is connected to the channel sweep/fine tuning input 3 of the frequency synthesizer unit 2. The wiper of the switch 14 is also connected to one input of an OR gate 17 whose output is connected to the input 4 of the synthesizer unit 2 whilst the wiper of the switch 15 is connected to one input of an OR gate 18 whose output is connected to the input 5 of the synthesizer unit 2.In the second position of each switch 14 and 15 the potentials applied to the terminals 8 and 9 are applied to the gate 16 and to the gates 17 and 18 respectively. The terminals 8 and 9 are also connected via respective switches 6 and 7 to respective inputs of an OR gate 19 whose output is operative to trigger a monostable multivibrator 20 the output of which is connected to one input of an AND gate 21 the other input of which is provided by a sync comparator 22 which is operative to compare the sync waveform in the video signal with the line flyback and provides a high output level when they are synchronised. The AND gate 21 have an output which is connected to provide a second input for each of the NOR gates 12 and 13.